Here is the second part of the RISC Processor Design. I have implemented this Processor as a part of my ASIC Design Lab project "Programmable Controller/Router and Peripheral Design with peripheral I/O multiplexing". This project focuses of peripheral multiplexing to the GPIO pins of the processor in runtime. An example case will be a Pulse Width Modulated wave switching between any I/O pins during processor execution or an UART Transmitter pin routed to a pin based on board design without the need of external multiplexers.

The processor can access the peripherals via register write instructions. Similar to register file, the peripherals support two data reads and one data write simultaneously. Since I have used custom instructions, a custom Instruction Set Architecture (ISA) is also designed.

16-bit Instruction Format :

1. Register Instruction:

OPCODE [15:12]

|

DEST[11:8]

|

SRC_1 [7:4]

|

SRC_2 [3:0]

|

2. Immediate Instruction:

OPCODE [15:12]

|

DEST[11:8]

|

Immediate [7:0]

|

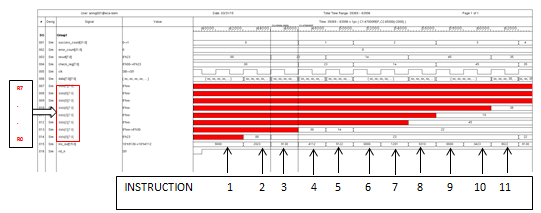

INSTRUCTION SET:

INSTRUCTION

|

OPCODE

|

INSTRUCTION

|

OPCODE

| |

NOP

|

0000

|

NOT

|

0111

| |

ADD

|

0001

|

MOV

|

1000

| |

ADDI

|

0010

|

MVI

|

1001

| |

SUB

|

0011

|

BC

|

1010

| |

SUBI

|

0100

|

BS

|

1011

| |

AND

|

0101

|

HLT

|

1111

| |

OR

|

0110

|

Comments

Post a Comment